VLSI SKILL SET

A SURVEY ON VLSI SKILL SET

(survey done till 11th dec,2020 11.59PM)

QUESTIONS AND RESPONSES OF SURVEY:

Design

flow:

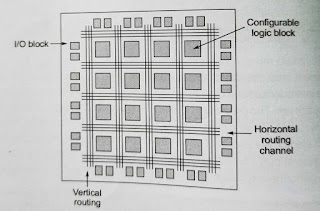

A design flow is a sequence of operations that transforms the IC

designers intension{ usually represented in RTl format} into layout. The design flow for a

typical IC project is shown in figure{2.4}.

CONCEPT AND MARKET RESEARCH:

A detailed research about the tools available for

designing the IC according to the speacification given in the requirements documents done

thoroughly.

Architecture specification and design constrains:

The design idea refined into a set of requirements is

known as specification. The general specification are,

1.What does the chip do?

2.How fast it need to operate in order to be

compititive in market?

3.How much power will it consume?

4.How big will it be?

HDL CAPTURE AND RTL COADING

The design of integrated allows the circuit{ICs} in an

art. During a half century of IC development, it has gradually become clear

that there is a need for a computer language to describre the structure and function of integrated

circuits, or for describing on entire electronic system. As a result, two HDL

languages, Verilog and VHDL, have been standardized and have emerged as the

tools for IC design.

An HDL is created to meet a number of needs in the

design process:

1:HDL allows the description of structure of a

hardware system.

2.HDL can be used to described how the system is

decomposed in to building blocks and how those building blocks are

interconnected.

3. It allows the specification of system functionally

by using the form of familiar programming languages.

4.The design of a system can be simulated before being

manufactured so that designers can quickly compare alternatives and test for

corrections without the delay and expense of hardware prototyping.

5.It allows the detailed structure of he design to be

synthesized from a more abstract specification, allowing the designers to

concentrate more on strategic design decisions. This automatic synthesis process

also helps reduce design implantation time.

LOGIC SIMULATION:

Simulation is the use of a computer programe to

simulate the operation of a digital circuit. logic stimulation is the primary

tool used for verifying the logical correctness of a hardware design. In many

logic simulation is the first activity performed in the process of taking a

hardware design from concept to realization . modern hardware description are

both simulatable and synthesizable.

LOGIC SYNTHESIS:

Logic synthesis is the process of translating an

abstract form of desired circuit behaviour { typically in RTL} into design

implementation in terms of logic gates.

LOGIC OPTIMIZATION:

Logic optimization a part of logic synthesis, is the

process of finding an equivalent representation of the specified logic circuit

under one or more specified constraints. Generally, the circuit is constrained

to minimum chip area meeting a prespesified delay. with the advent of net list reprentation

of the given design description. Today , logic optimization is devided in to

various categories based on two criteria:

BASED ON CIRCIUT REPRESNTATION :

1.Two -level logic optimization

2.Multi-level logic optimization.

BASED ON CIRCUIT CHARACTERISTICS:

1.Sequential logic optimization.

2.Combinational logic optimization.

FORMAL VERIFICATION:

Reification is the process of cheaking the designs

functional correctness. This process can consume over 60% of the total design

resoures in todays large , complicated chip designs.

Formal verifications techniques perform validation of

a design using mathematical methods without the need for technological

considerations, such as timing and physical effects. they chaeck for logical

functions of a designed by comparing it against the reference design.

The perpose of the formal verification in the design

flow is to validate the RTL against RTL ,gate-level netlist against the RTL

code, or the comparison between gate-level netlists. The RTL to RTL verification

is used to validate the new RTL against

the old functionally correct RTL . this is usually performed fpr designed that

are subject to frequent changes in order to accommodate additional features.

When these features are added to the sourse RTL ,here is always a risk of

breaking the old functionally correct features .To prevent this, formal verification

may be perform between the old RTL and the new RTL to check the validity of the

old functionality.

STATIC TIMING ANALYSIS:

Static timing analysis {STA} is a method of computing

the expected timing of signals inside a digital circuit without using

stimulation.

STA is not designed for verifying the designs

functional correctness but to cheak its timing validity .it locates the worst case delay of the circuit over all possible

input combinations. There are huge numbers of logic path inside a chip of

complex design. The advantages of STA is that itperforms timimg analysis on all

possible paths. In other words , unlike simulation, which only cheak timing on

given paths, STAis a complete timing cheak all that cover of the paths,

wheather they are real or potential false paths

Author name:

Rohan Awale

Ref:

NPTEL Lec of Digital Design

Good information!

ReplyDeleteInformative!

ReplyDeleteVery informative !!!

ReplyDeleteok

DeleteGreat content on VLSI skill set!

ReplyDeleteVery well explained. keep it up

ReplyDeletethank you

DeleteNice writing, well explained. Keep it up!!

ReplyDeletethak you and in coming weeks i will definietly post such type of blogs

DeleteInformative blog

ReplyDeletethanks for appreciation.

DeleteKeep it up very informative

ReplyDeletethank you for appreciation

Deletevery useful!!

ReplyDeleteVery Nice information.

ReplyDeleteWell explained. Keep it up

ReplyDeleteInformative👍

ReplyDeletethank you

DeleteVery informative blog..many things to get learn from this...keep it up👍

ReplyDeletethank you for appreciation , in coming weeks i will posting such type post so do read that one also

DeleteGreat work!!!

ReplyDeletethank you for appreciation

DeleteAwesome👍👏

ReplyDeleteGreat work!!!!!

ReplyDelete👍👍good informative content

ReplyDeleteA survey giving us the complete idea about the skills required in VLSI. Well done.

ReplyDeletethank you and i coming days we will postiing such type of blog on some another concept of VLSI do read it.

DeleteGreat to have such valuable information at one place

ReplyDeletethank you for appreciation.

DeleteInformative 👍

ReplyDeleteok

DeleteVery informative content bro , it was very helpful and Easy to understand too.... great work !!

ReplyDeleteAll my doubt are cleared , well explained. Thank you 👍

ReplyDeletereally thank you , as my this small content helps you it motivates me in my further tasks.

DeleteVery insightful!

ReplyDeletethank you

DeleteVery informative!

ReplyDeleteGood

ReplyDeleteVery informative

ReplyDeleteVery informative 👍

ReplyDeleteVery informative! 👍

ReplyDeleteInformative

ReplyDeleteGreat work!!

ReplyDeleteNicely written!!

ReplyDeleteGot too know about latest Industrial needs.. Well written

ReplyDeletethank you for appreciation and in coming days i will posting such latest things happen in VLSI industry do read it.

DeleteVery informative 👍

ReplyDeleteGood work!

ReplyDeleteNice work

ReplyDeleteInformative!!

ReplyDeleteGood information

ReplyDeleteVery nicely Explained about VLSI skill sets ✨

ReplyDeleteExcellent..... Keep it up 👍👍

ReplyDeleteVery informative content! Got to learn many things about vlsi

ReplyDeletethank you for appreciation

DeleteInformative content keep it up

ReplyDeleteInformative blog

ReplyDeleteExcellent information...!!!

ReplyDeleteKeep it up..👍👍

Very informative blog...got better understanding in VLSI design...please suggest some important part of VLSI DESIGN

ReplyDeletethere as such not any imp point , it is whole concept very important from the point of VLSI

DeleteGood research and very informative

ReplyDeleteNice explanation Rohan sir...!!!

ReplyDeleteKeep it up..and do posting such helpful good content blogs.. really help this!!

Yes...sure also I am learning about new adv.

DeleteThings regarding it.. definitely I will publish.

That's great 🔥👍🏻

ReplyDeleteVery insightful

ReplyDeleteGreat work!

ReplyDeleteVery well presented. Nice work

ReplyDeletethank you

DeleteVery informative!

ReplyDeleteVery good illustration using the pie chart. Keep it up

ReplyDeleteNice explanation Rohan bhai...!!!

ReplyDeleteKeep it up..and do posting such helpful good content blogs.. really help this!!

thank you so much for the appreciation

DeleteExcellent

ReplyDeleteGreat work bro

ReplyDeleteGood work

ReplyDeleteVery informative

ReplyDeleteVery informative

ReplyDeleteVery informative

ReplyDelete